Federico Busato

# High-Performance and Power-Aware Graph Processing on GPUs

Ph.D. Thesis

January 13, 2018

Università degli Studi di Verona Dipartimento di Informatica Advisor: prof. Nicola Bombieri

Series  $N^{\circ}$ : ???? (ask the PhD coordinator!)

Università di Verona Dipartimento di Informatica Strada le Grazie 15, 37134 Verona Italy

# Contents

| 1 | Thesis Abstract | 1 |

|---|-----------------|---|

|   |                 |   |

## Part I Background

| <b>2</b> | Graphic Processing Unit (GPU)                  | 11 |

|----------|------------------------------------------------|----|

|          | .1 Computed Unified Device Architecture (CUDA) | 11 |

|          | .2 Modern GPU architectures 1                  | 13 |

|          |                                                |    |

|          |                                                |    |

| 3        | tatic Graph Representation                     | 15 |

| 3        | Static Graph Representation                    |    |

| 3        |                                                | 15 |

# Part II Performance-Oriented Implementations of Graph Algorithms for GPU

| 4        | Rela | ted Work                                      |

|----------|------|-----------------------------------------------|

|          | 4.1  | The workload partitioning problem in GPUs 25  |

|          |      | 4.1.1 Static mapping techniques               |

|          |      | 4.1.2 Semi-dynamic mapping techniques         |

|          |      | 4.1.3 Dynamic mapping techniques 31           |

|          | 4.2  | Graph Traversal and Breadth-First Search      |

|          | 4.3  | Single-Source Shortest Path 35                |

|          | 4.4  | Strongly Connected Components 36              |

|          |      | 4.4.1 FORWARD-BACKWARD algorithm              |

|          |      | 4.4.2 Coloring algorithm                      |

|          |      | 4.4.3 Other algorithms                        |

| <b>5</b> | Loa  | d Balancing - Multi-Phase Search Algorithm 41 |

|          | 5.1  | Introduction                                  |

|          | 5.2  | The proposed Multi-phase Mapping 43           |

|          |      | 5.2.1 Hybrid partitioning 43                  |

| VI | Contents |

|----|----------|

| VI | Contents |

|   |     | 5.2.2 Iterative Coalesced Expansion 4                                                                           | 45        |

|---|-----|-----------------------------------------------------------------------------------------------------------------|-----------|

|   |     | 5.2.3 Optimizing the Multi-Phase implementation 4                                                               | 47        |

|   | 5.3 | Comprehensive comparison of complexity and limiting factors of                                                  |           |

|   |     |                                                                                                                 | 49        |

|   | 5.4 |                                                                                                                 | 52        |

|   |     | 5.4.1 Multi-phase Mapping Analisys 5                                                                            | 58        |

|   | 5.5 | • •                                                                                                             | 60        |

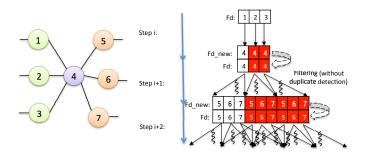

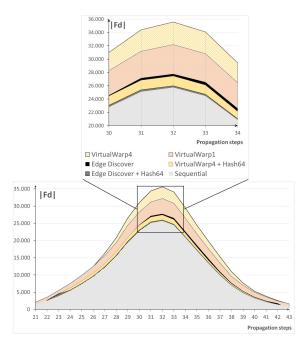

| 6 | Bre | adth-First Search - BFS-4K                                                                                      | 61        |

|   | 6.1 |                                                                                                                 | 61        |

|   |     |                                                                                                                 | <b>53</b> |

|   | 6.2 |                                                                                                                 | 63        |

|   | 6.3 | I · · · · · · · · · · · · · · · · · · ·                                                                         | 65        |

|   |     |                                                                                                                 | 65        |

|   |     | 1                                                                                                               | 66        |

|   |     |                                                                                                                 | 67        |

|   |     | 0                                                                                                               | <u> </u>  |

|   |     |                                                                                                                 | 71        |

|   |     |                                                                                                                 | 72        |

|   | 6.4 |                                                                                                                 | 74        |

|   | 6.5 | I · · · · · · · · · · · · · · · · · · ·                                                                         | 77        |

|   | 6.6 | Concluding remarks 8                                                                                            | 82        |

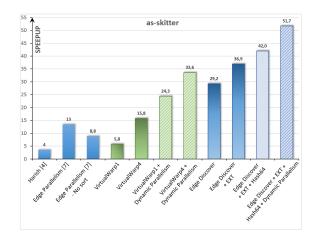

| 7 | Bre |                                                                                                                 | 83        |

|   | 7.1 |                                                                                                                 | 33        |

|   | 7.2 | 01                                                                                                              | 84        |

|   | 7.3 |                                                                                                                 | 85        |

|   |     | 8                                                                                                               | 86        |

|   |     |                                                                                                                 | 88        |

|   |     | 1 01                                                                                                            | 90        |

|   |     |                                                                                                                 | 90        |

|   |     |                                                                                                                 | 91        |

|   |     |                                                                                                                 | 91        |

|   |     | The second se | 92        |

|   |     | 0 0                                                                                                             | 92        |

|   |     |                                                                                                                 | 93        |

|   |     |                                                                                                                 | 94        |

|   | 7.4 | 1                                                                                                               | 95        |

|   |     | 1 v 1                                                                                                           | 95        |

|   |     |                                                                                                                 | 96        |

|   |     | 7.4.3 Performance evaluation                                                                                    |           |

|   | 7.5 | Conclusions                                                                                                     |           |

|   | 7.6 | Appendix                                                                                                        | 11        |

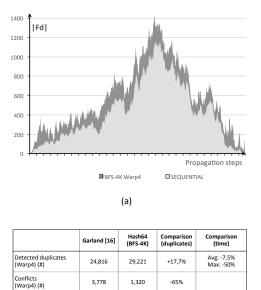

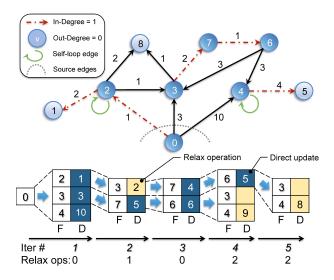

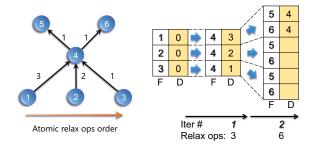

| 8  | Sing | gle-Source Shortest Path - H-BF                                   |       |

|----|------|-------------------------------------------------------------------|-------|

|    | 8.1  | Introduction                                                      |       |

|    | 8.2  | The Bellman-Ford's algorithm                                      |       |

|    | 8.3  | The frontier-based algorithm and its optimizations                |       |

|    |      | 8.3.1 The edge classification optimization                        |       |

|    |      | 8.3.2 $$ Duplicate removal with Kepler 64-bit atomic instructions |       |

|    | 8.4  | Architecture-oriented Optimizations                               |       |

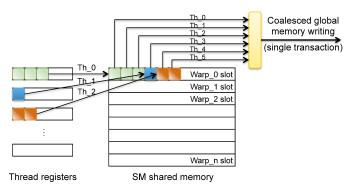

|    |      | 8.4.1 $$ Memory coalescing, cache modifiers, and texture memory   | . 113 |

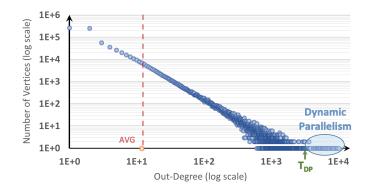

|    |      | 8.4.2 Dynamic virtual warps                                       | . 114 |

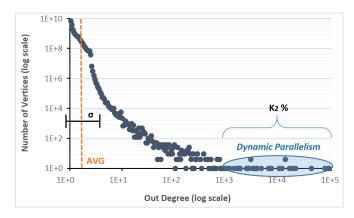

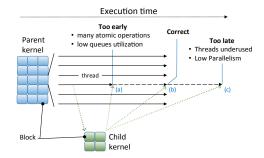

|    |      | 8.4.3 Dynamic parallelism                                         | . 116 |

|    | 8.5  | Experimental Results                                              | . 116 |

|    |      | 8.5.1 Experimental setup                                          | . 116 |

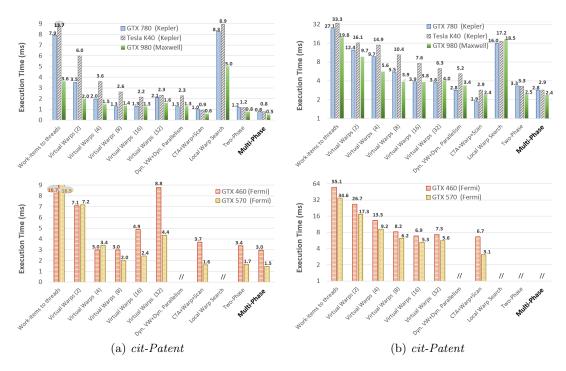

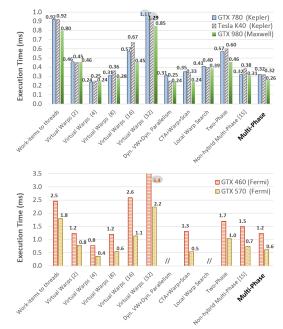

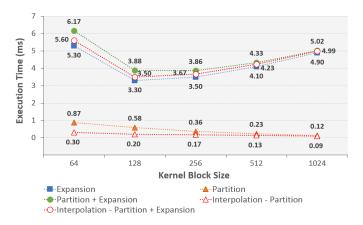

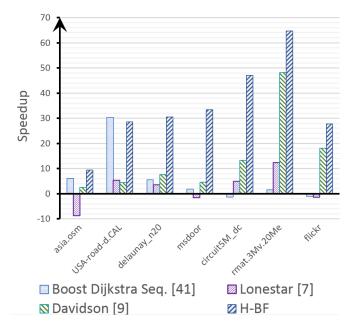

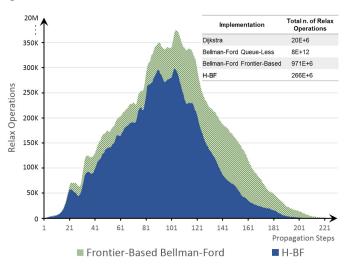

|    |      | 8.5.2 Execution time analysis and comparison                      | . 117 |

|    | 8.6  | Concluding Remarks                                                | . 120 |

|    | ~    |                                                                   |       |

| 9  |      | ongly Connected Components - Multi-Step Algorithm                 |       |

|    | 9.1  | Introduction                                                      |       |

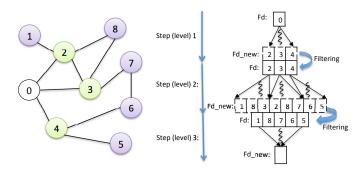

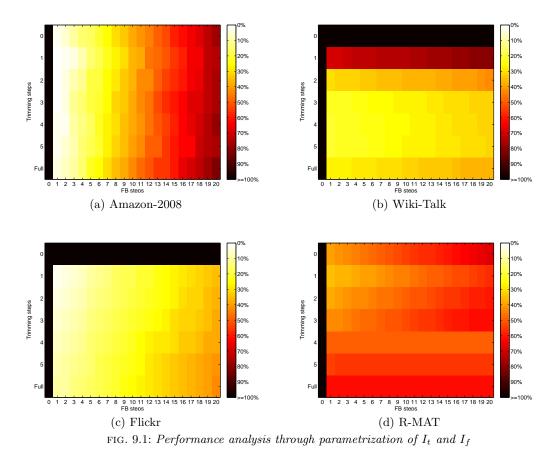

|    | 9.2  | Multi-step Parametric Scheme for SCC Decomposition                |       |

|    |      | 9.2.1 Parallelization strategy for graph traversal                |       |

|    | 9.3  | Experimental results                                              |       |

|    | 9.4  | Conclusions                                                       | . 131 |

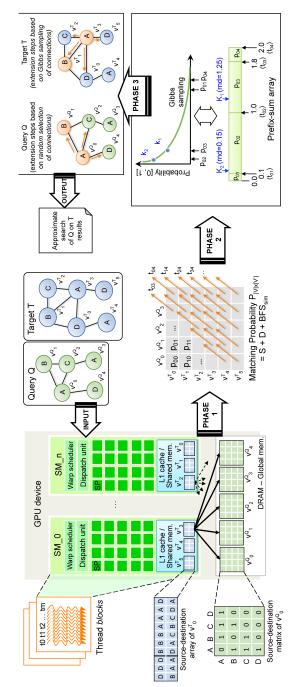

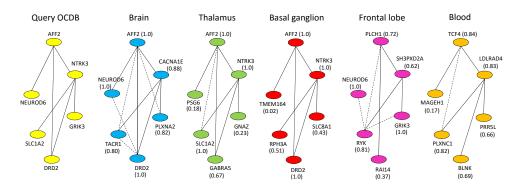

| 10 | App  | proximate Subgraph Isomorphism - APPAGATO                         | . 133 |

|    |      | Materials and methods                                             |       |

|    |      | 10.1.1 Definitions and notations                                  |       |

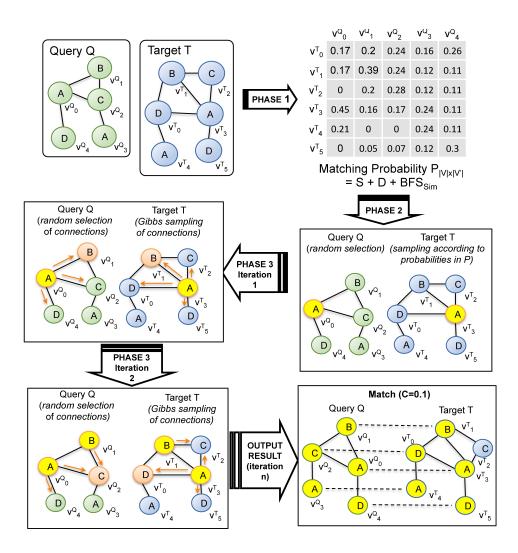

|    |      | 10.1.2 The APPAGATO algorithm                                     | . 134 |

|    |      | 10.1.3 The APPAGATO parallel implementation for GPUs              | . 138 |

|    |      | 10.1.4 Datasets                                                   | . 141 |

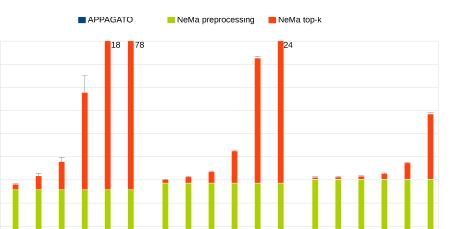

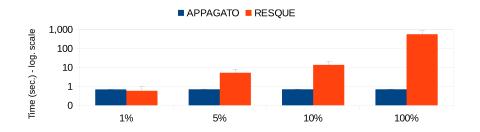

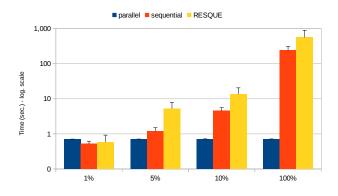

|    | 10.2 | Results and discussion                                            | . 142 |

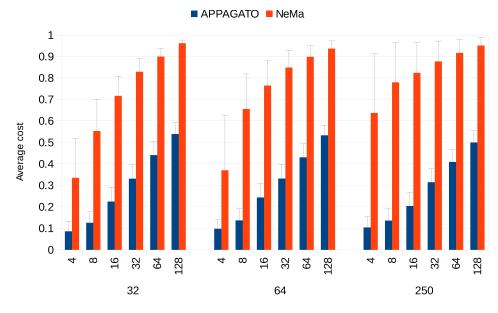

|    |      | 10.2.1 Performance                                                | . 142 |

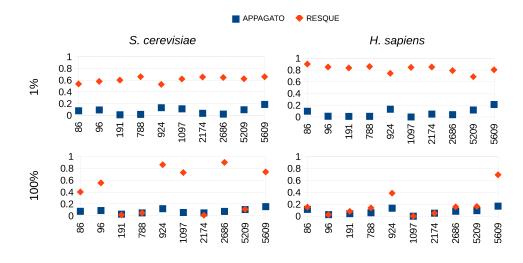

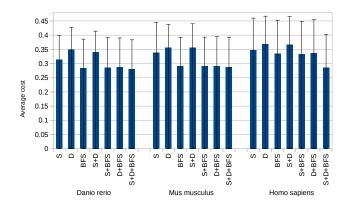

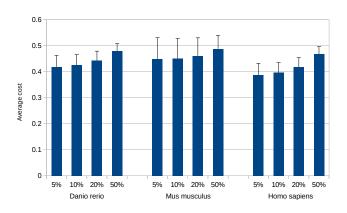

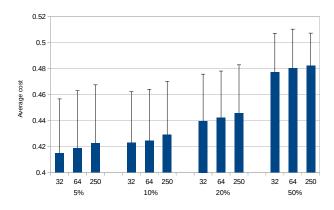

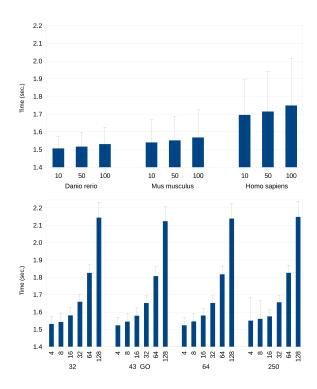

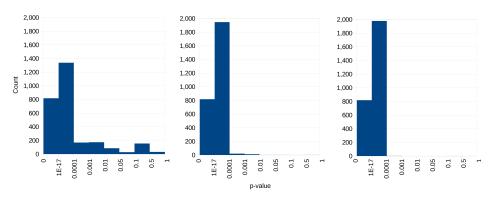

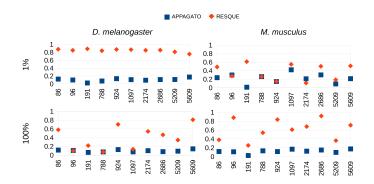

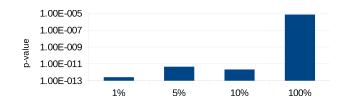

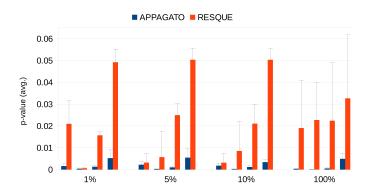

|    |      | 10.2.2 Quality measurements of matches                            | . 143 |

|    |      | 10.2.3 Querying protein complexes among different species         | . 144 |

|    |      | 10.2.4 Datasets and query details                                 | . 145 |

|    | 10.3 | APPAGATO Implementation                                           |       |

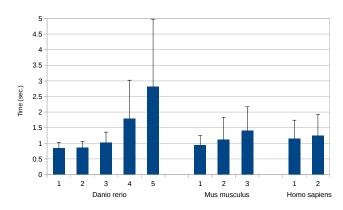

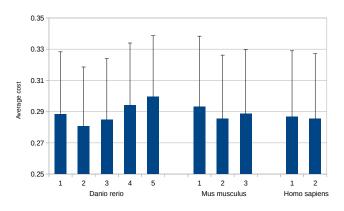

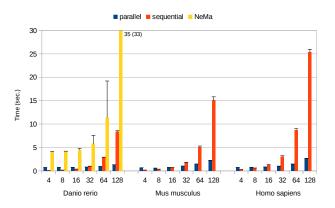

|    |      | 10.3.1 APPAGATO performance                                       |       |

|    | 10.4 | Functional coherence measurement in querying protein complexes    |       |

|    |      | among different species.                                          | . 153 |

|    |      | 10.4.1 Querying disease modules                                   |       |

|    | 10.5 | Conclusions                                                       |       |

# Part III Profiling and Analysis Framework

| 11 | Related Work               | 165   |

|----|----------------------------|-------|

|    | 11.1 Performance models    | . 165 |

|    | 11.2 GPU Microbenchmarking | 166   |

## VIII Contents

| <b>12</b> | Par                                  | allel Primitives Profiling169                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 12.1                                 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           | 12.2                                 | Profiler Metrics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           | 12.3                                 | Optimization Criteria                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

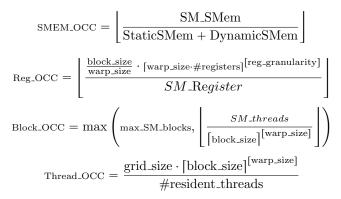

|           |                                      | 12.3.1 Occupancy (OCC)173                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|           |                                      | 12.3.2 Host Synchronization (HSync)174                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           |                                      | 12.3.3 Device Synchronization (DSync)175                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|           |                                      | 12.3.4 Thread Divergence (TDiv)175                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|           |                                      | 12.3.5 Warp Load Balancing $(LB_W)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|           |                                      | 12.3.6 Streaming Multiprocessor Load Balancing $(LB_{SM})$ 176                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|           |                                      | 12.3.7 L1/L2 Granularity $(Gran_{L1}/Gran_{L2})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

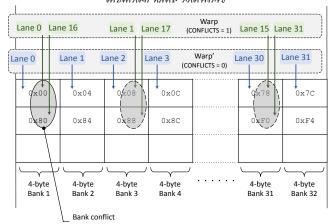

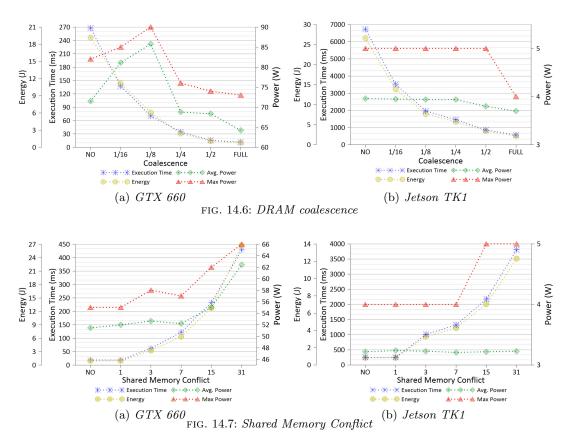

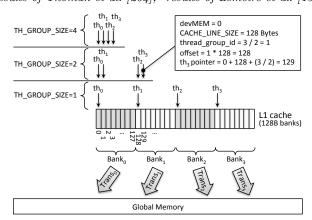

|           |                                      | 12.3.8 Shared Memory Efficiency (SMem <sub>eff</sub> )177                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|           |                                      | 12.3.9 Computation Intensity (CI)177                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|           |                                      | 12.3.10Data Transfer (DT)177                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|           |                                      | 12.3.11Overall Quality Metrics (QM)178                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|           | 12.4                                 | Weighing of Optimization Criteria on the Overall Quality Metrics . 178                                                                                                                                                                                                                                                                                                                                                                                                                                           |

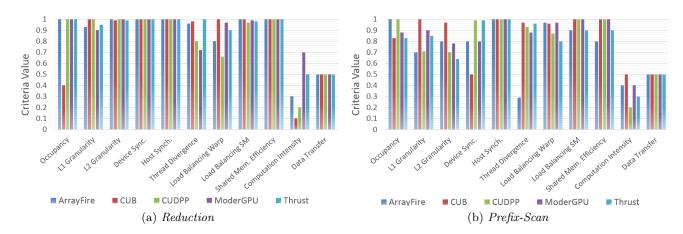

|           |                                      | 12.4.1 Parallel Primitives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|           |                                      | 12.4.2 Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | 12.5                                 | Case Studies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

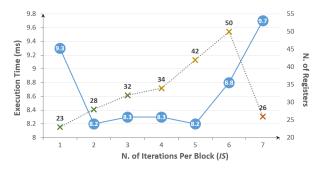

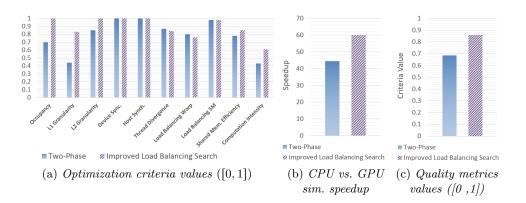

|           |                                      | 12.5.1 The Load Balancing Search Primitive                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

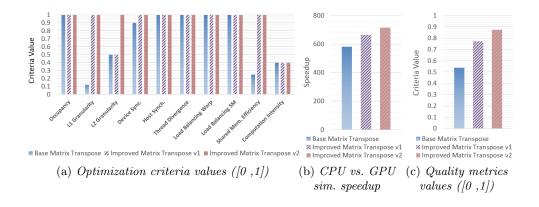

|           |                                      | 12.5.2 The <i>Matrix Transpose</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|           | 12.6                                 | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 10        |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12        |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 13        |                                      | ine-grained Performance Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10        | 13.1                                 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15        | 13.1                                 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 10        | 13.1                                 | Introduction187Microbenchmarks18913.2.1Microbenchmark Development190                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 15        | $13.1 \\ 13.2$                       | Introduction187Microbenchmarks18913.2.1Microbenchmark Development19013.2.2GPU Device Characterization through Microbenchmarks190                                                                                                                                                                                                                                                                                                                                                                                 |

| 10        | $13.1 \\ 13.2$                       | Introduction187Microbenchmarks18913.2.1Microbenchmark Development19013.2.2GPU Device Characterization through Microbenchmarks190Optimization Criteria191                                                                                                                                                                                                                                                                                                                                                         |

| 10        | $13.1 \\ 13.2$                       | Introduction187Microbenchmarks18913.2.1Microbenchmark Development19013.2.2GPU Device Characterization through Microbenchmarks190Optimization Criteria19113.3.1Host Synchronization192                                                                                                                                                                                                                                                                                                                            |

| 10        | $13.1 \\ 13.2$                       | Introduction187Microbenchmarks18913.2.1Microbenchmark Development19013.2.2GPU Device Characterization through Microbenchmarks190Optimization Criteria19113.3.1Host Synchronization19213.3.2Device Synchronization192                                                                                                                                                                                                                                                                                             |

| 10        | $13.1 \\ 13.2$                       | Introduction187Microbenchmarks18913.2.1Microbenchmark Development19013.2.2GPU Device Characterization through Microbenchmarks190Optimization Criteria19113.3.1Host Synchronization19213.3.2Device Synchronization19213.3.3Thread Divergence192                                                                                                                                                                                                                                                                   |

| 19        | $13.1 \\ 13.2$                       | Introduction187Microbenchmarks18913.2.1Microbenchmark Development19013.2.2GPU Device Characterization through Microbenchmarks190Optimization Criteria19113.3.1Host Synchronization19213.3.2Device Synchronization19213.3.3Thread Divergence19213.3.4Warp Load Balancing193                                                                                                                                                                                                                                       |

| 19        | $13.1 \\ 13.2$                       | Introduction187Microbenchmarks18913.2.1Microbenchmark Development19013.2.2GPU Device Characterization through Microbenchmarks190Optimization Criteria19113.3.1Host Synchronization19213.3.2Device Synchronization19213.3.3Thread Divergence19213.3.4Warp Load Balancing19313.3.5Streaming Multiprocessor (SM) Load Balancing193                                                                                                                                                                                  |

| 10        | $13.1 \\ 13.2$                       | Introduction187Microbenchmarks18913.2.1Microbenchmark Development19013.2.2GPU Device Characterization through Microbenchmarks190Optimization Criteria19113.3.1Host Synchronization19213.3.2Device Synchronization19213.3.3Thread Divergence19213.3.4Warp Load Balancing19313.3.5Streaming Multiprocessor (SM) Load Balancing19313.3.6L1/L2Granularity193                                                                                                                                                         |

| 10        | $13.1 \\ 13.2$                       | Introduction187Microbenchmarks18913.2.1Microbenchmark Development19013.2.2GPU Device Characterization through Microbenchmarks190Optimization Criteria19113.3.1Host Synchronization19213.3.2Device Synchronization19213.3.3Thread Divergence19213.3.4Warp Load Balancing19313.3.5Streaming Multiprocessor (SM) Load Balancing19313.3.7Shared Memory Efficiency194                                                                                                                                                 |

| 19        | 13.1<br>13.2<br>13.3                 | Introduction187Microbenchmarks18913.2.1Microbenchmark Development19013.2.2GPU Device Characterization through Microbenchmarks190Optimization Criteria19113.3.1Host Synchronization19213.3.2Device Synchronization19213.3.3Thread Divergence19213.3.4Warp Load Balancing19313.3.5Streaming Multiprocessor (SM) Load Balancing19313.3.7Shared Memory Efficiency19413.3.8Throughput/Occupancy194                                                                                                                    |

| 19        | 13.1<br>13.2<br>13.3                 | Introduction187Microbenchmarks18913.2.1Microbenchmark Development19013.2.2GPU Device Characterization through Microbenchmarks190Optimization Criteria19113.3.1Host Synchronization19213.3.2Device Synchronization19213.3.3Thread Divergence19213.3.4Warp Load Balancing19313.3.5Streaming Multiprocessor (SM) Load Balancing19313.3.7Shared Memory Efficiency19413.3.8Throughput/Occupancy194Performance Prediction195                                                                                           |

| 19        | 13.1<br>13.2<br>13.3                 | Introduction187Microbenchmarks18913.2.1Microbenchmark Development19013.2.2GPU Device Characterization through Microbenchmarks190Optimization Criteria19113.3.1Host Synchronization19213.3.2Device Synchronization19213.3.3Thread Divergence19213.3.4Warp Load Balancing19313.3.5Streaming Multiprocessor (SM) Load Balancing19313.3.6L1/L2Granularity19313.3.7Shared Memory Efficiency19413.3.8Throughput/Occupancy194Performance Prediction195Experimental Results196                                           |

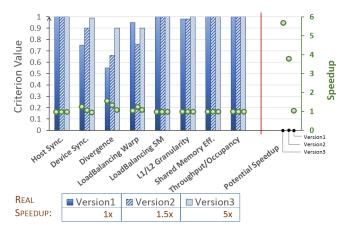

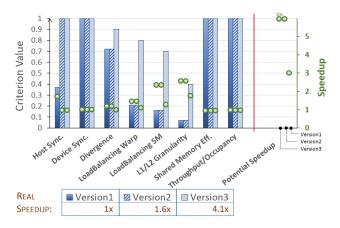

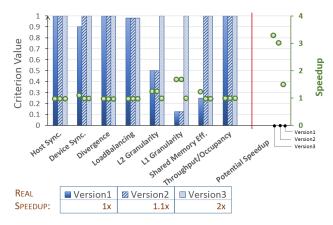

| 19        | 13.1<br>13.2<br>13.3                 | Introduction187Microbenchmarks18913.2.1Microbenchmark Development19013.2.2GPU Device Characterization through Microbenchmarks190Optimization Criteria19113.3.1Host Synchronization19213.3.2Device Synchronization19213.3.3Thread Divergence19213.3.4Warp Load Balancing19313.3.5Streaming Multiprocessor (SM) Load Balancing19313.3.6L1/L2 Granularity19313.3.8Throughput/Occupancy194Performance Prediction195Experimental Results19613.5.1Case study 1: Parallel Reduction196                                  |

| 19        | 13.1<br>13.2<br>13.3                 | Introduction187Microbenchmarks18913.2.1Microbenchmark Development19013.2.2GPU Device Characterization through Microbenchmarks190Optimization Criteria19113.3.1Host Synchronization19213.3.2Device Synchronization19213.3.3Thread Divergence19213.3.4Warp Load Balancing19313.3.5Streaming Multiprocessor (SM) Load Balancing19313.3.7Shared Memory Efficiency19413.3.8Throughput/Occupancy194Performance Prediction195Experimental Results19613.5.1Case study 1: Parallel Reduction19613.5.2Case study 2: BFS197 |

| 19        | 13.1<br>13.2<br>13.3<br>13.4<br>13.4 | Introduction187Microbenchmarks18913.2.1Microbenchmark Development19013.2.2GPU Device Characterization through Microbenchmarks190Optimization Criteria19113.3.1Host Synchronization19213.3.2Device Synchronization19213.3.3Thread Divergence19213.3.4Warp Load Balancing19313.3.5Streaming Multiprocessor (SM) Load Balancing19313.3.6L1/L2 Granularity19313.3.8Throughput/Occupancy194Performance Prediction195Experimental Results19613.5.1Case study 1: Parallel Reduction196                                  |

| <b>14</b> | Power/Performance/Energy Microbenchmarking                        |

|-----------|-------------------------------------------------------------------|

|           | 14.1 Introduction                                                 |

|           | 14.2 The Microbenchmark Suite                                     |

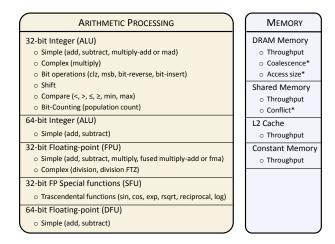

|           | 14.2.1 Arithmetic processing benchmarks                           |

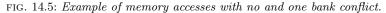

|           | 14.2.2 Memory benchmarks                                          |

|           | 14.3 Experimental Results                                         |

|           | 14.4 Conclusions                                                  |

| 15        | Power-aware Performance Tuning of GPU Applications                |

|           | Through Microbenchmarking                                         |

|           | 15.1 Introduction                                                 |

|           | 15.2 The Microbenchmark Suite                                     |

|           | 15.2.1 GPU static characteristics                                 |

|           | 15.2.2 GPU dynamic characteristics                                |

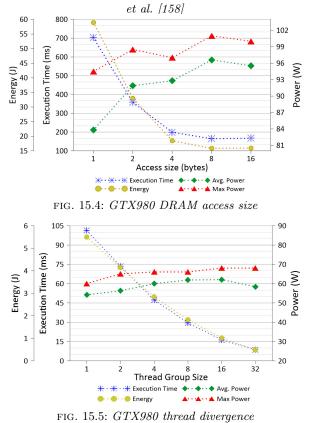

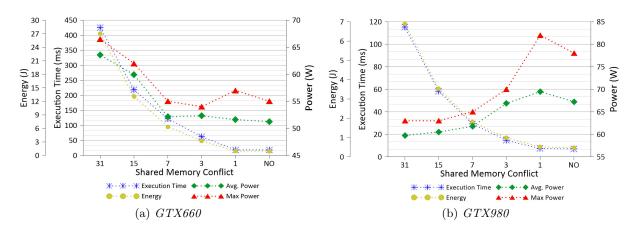

|           | 15.3 Experimental Results                                         |

|           | 15.3.1 GPU Device Characterization                                |

|           | 15.3.2 Vector Reduction                                           |

|           | 15.3.3 Matrix Transpose                                           |

|           | 15.4 Conclusions                                                  |

| 16        | A Performance, Power, and Energy Efficiency Analysis of           |

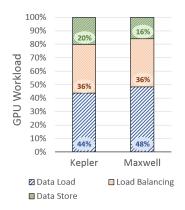

|           | Load Balancing Techniques for GPUs                                |

|           | 16.1 Introduction                                                 |

|           | 16.1.1 The <i>Multi-phase</i> technique                           |

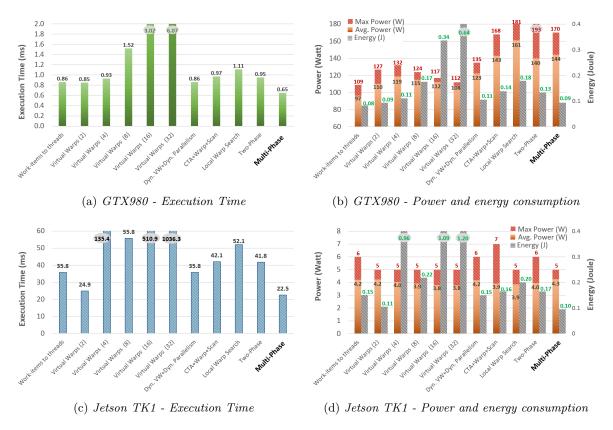

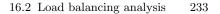

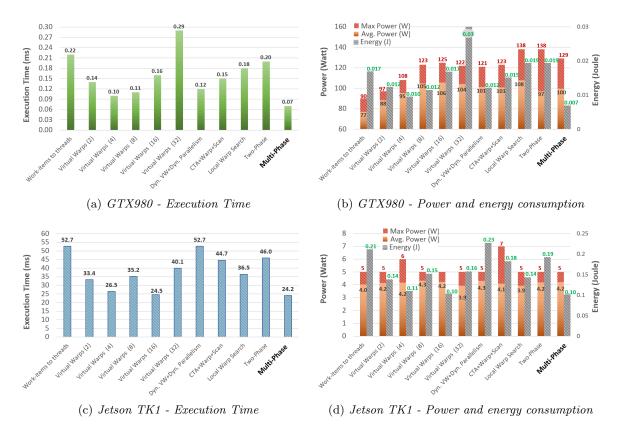

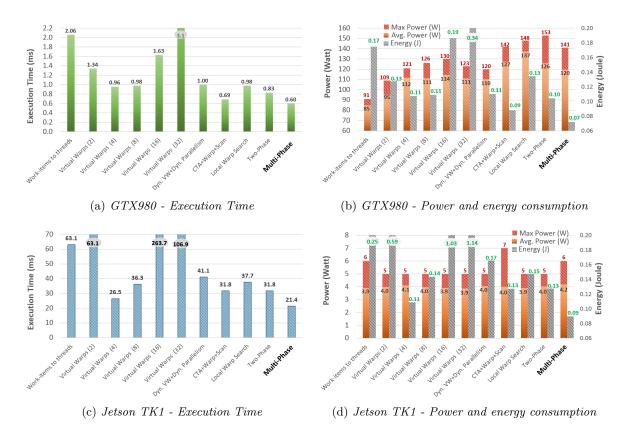

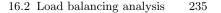

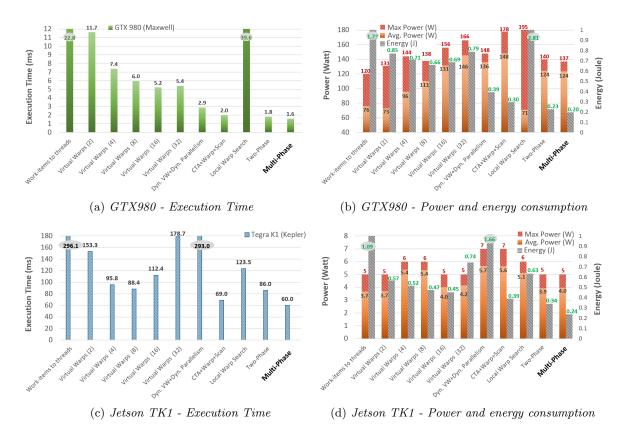

|           | 16.2 Load balancing analysis                                      |

|           | 16.2.1 Characteristics of datasets, GPU devices, and equipment    |

|           | for performance, power, energy efficiency measurement $\dots 231$ |

|           | 16.2.2 Performance, power, energy efficiency analysis             |

|           | 16.3 Conclusion                                                   |

|           | 10.5 Coliciusion                                                  |

## Part IV Dynamic Graph Processing

| 17 | Related Work                                                                                                                                   |

|----|------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 17.0.1 Dynamic Sparse Formats                                                                                                                  |

|    | 17.0.2 K-Truss                                                                                                                                 |

|    | 17.0.3 Triangle Counting                                                                                                                       |

|    | 17.0.4 GPU Triangle Counting                                                                                                                   |

|    | 17.0.5 Streaming and Dynamic Triangle Counting                                                                                                 |

|    |                                                                                                                                                |

| 18 | Hornet: An Efficient Data Structure for Dynamic Sparse                                                                                         |

| 18 | Graphs and Matrices                                                                                                                            |

| 18 | Graphs and Matrices24918.1 Introduction24918.2 Hornet Overview250                                                                              |

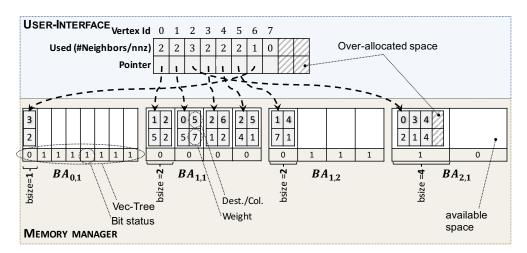

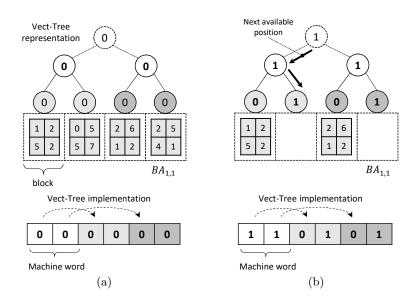

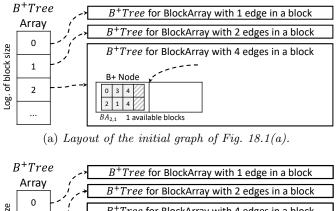

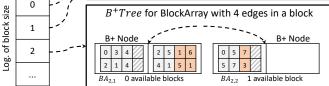

| 18 | Graphs and Matrices       249         18.1 Introduction       249         18.2 Hornet Overview       250         18.2.1 Block arrays       253 |

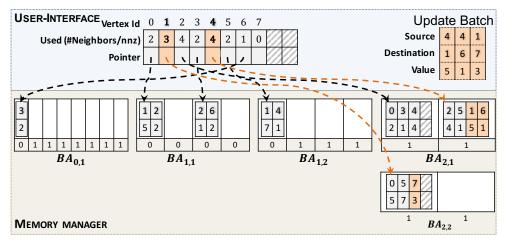

|    | 18.2.5 Dynamic Updates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3                                              |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

|    | 18.2.6 Handling graphs with extra properties                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3                                              |

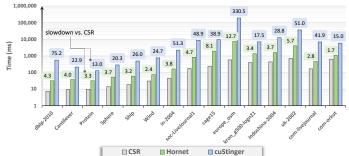

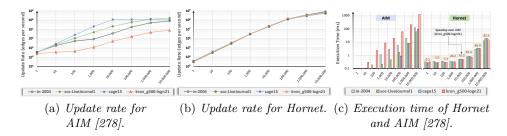

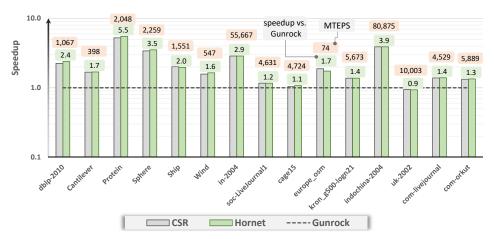

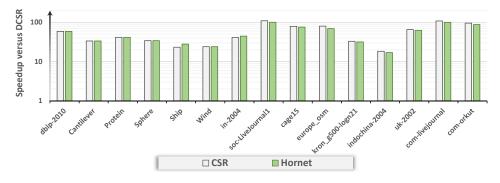

|    | 18.3 Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9                                              |

|    | 18.4 The Hornet data structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | )                                              |

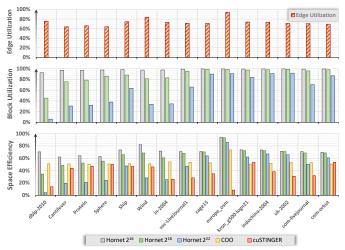

|    | 18.4.1 Memory utilization efficiency                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | )                                              |

|    | 18.4.2 Initialization Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                |

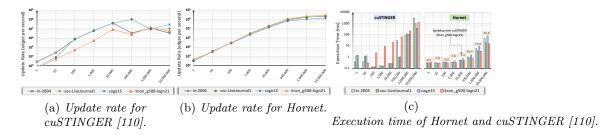

|    | 18.4.3 Update rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                |

|    | 18.4.4 Dynamic Triangle Counting                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                |

|    | 18.4.5 Breadth-first search                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                |

|    | 18.4.6 SpMV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                |

|    | 18.5 Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                                              |

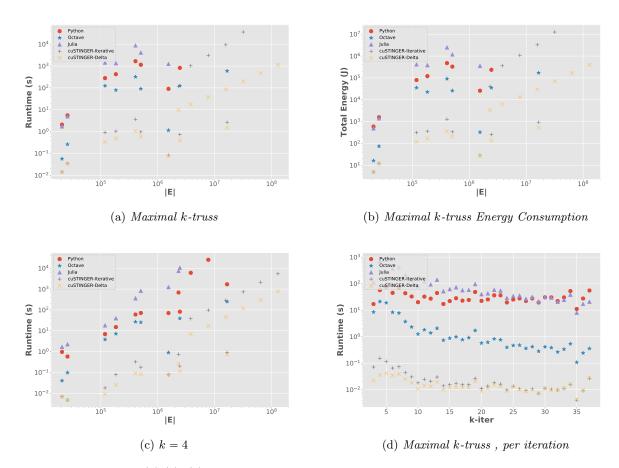

| 19 | Quickly Finding a Truss in a Haystack                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7                                              |

| 19 | Quickly Finding a Truss in a Haystack       267         19.1 Introduction       267                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                |

| 19 | 19.1 Introduction26719.2 KTruss Algorithm Using Dynamic Graphs268                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7<br>8                                         |

| 19 | 19.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7<br>8                                         |

| 19 | 19.1 Introduction26719.2 KTruss Algorithm Using Dynamic Graphs268                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7<br>8<br>9                                    |

| 19 | 19.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7<br>8<br>9<br>9                               |

| 19 | 19.1 Introduction       267         19.2 KTruss Algorithm Using Dynamic Graphs       268         19.2.1 Problem Definition       269         19.3 Proposed Algorithm       269                                                                                                                                                                                                                                                                                                                           | 7<br>8<br>9<br>9                               |

| 19 | 19.1 Introduction       267         19.2 KTruss Algorithm Using Dynamic Graphs       268         19.2.1 Problem Definition       269         19.3 Proposed Algorithm       269         19.3.1 Triangle Subtraction       269                                                                                                                                                                                                                                                                             | 7<br>8<br>9<br>9<br>9                          |

| 19 | 19.1 Introduction       267         19.2 KTruss Algorithm Using Dynamic Graphs       268         19.2.1 Problem Definition       269         19.3 Proposed Algorithm       269         19.3.1 Triangle Subtraction       269         19.3.2 Triangle Detection For Single Edge-Pair Deletions       270                                                                                                                                                                                                  | 7<br>8<br>9<br>9<br>9<br>0                     |

| 19 | 19.1 Introduction       267         19.2 KTruss Algorithm Using Dynamic Graphs       268         19.2.1 Problem Definition       269         19.3 Proposed Algorithm       269         19.3.1 Triangle Subtraction       269         19.3.2 Triangle Detection For Single Edge-Pair Deletions       270         19.3.3 Triangle Detection For Dual Edge-Pair Deletions       271                                                                                                                         | 7<br>8<br>9<br>9<br>9<br>9<br>9<br>0<br>1      |

| 19 | 19.1 Introduction       267         19.2 KTruss Algorithm Using Dynamic Graphs       268         19.2.1 Problem Definition       269         19.3 Proposed Algorithm       269         19.3.1 Triangle Subtraction       269         19.3.2 Triangle Detection For Single Edge-Pair Deletions       270         19.3.3 Triangle Detection For Dual Edge-Pair Deletions       271         19.4 Experimental Results       271                                                                             | 7<br>8<br>9<br>9<br>9<br>0<br>1<br>1<br>2      |

| 19 | 19.1 Introduction       265         19.2 KTruss Algorithm Using Dynamic Graphs       268         19.2.1 Problem Definition       269         19.3 Proposed Algorithm       269         19.3.1 Triangle Subtraction       269         19.3.2 Triangle Detection For Single Edge-Pair Deletions       270         19.3.3 Triangle Detection For Dual Edge-Pair Deletions       271         19.4 Experimental Results       271         19.4.1 Dynamic Graphs       272                                     | 7<br>8<br>9<br>9<br>9<br>0<br>1<br>1<br>2<br>2 |

| 19 | 19.1 Introduction       265         19.2 KTruss Algorithm Using Dynamic Graphs       268         19.2.1 Problem Definition       269         19.3 Proposed Algorithm       269         19.3.1 Triangle Subtraction       269         19.3.2 Triangle Detection For Single Edge-Pair Deletions       270         19.3.3 Triangle Detection For Dual Edge-Pair Deletions       271         19.4 Experimental Results       272         19.4.1 Dynamic Graphs       272         19.4.2 Benchmarks       272 | 78999011223                                    |

## Part V Applications

| 20        | Invariant Mining                                                   |

|-----------|--------------------------------------------------------------------|

|           | 20.1 Introduction                                                  |

|           | 20.2 Preliminary definitions                                       |

|           | 20.3 Invariant mining                                              |

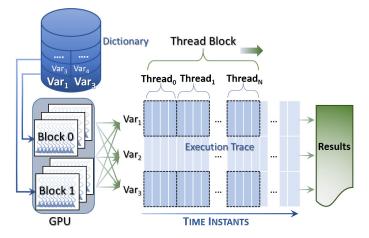

|           | 20.3.1 The parallel implementation for GPUs                        |

|           | 20.3.2 Generation of the variable dictionary                       |

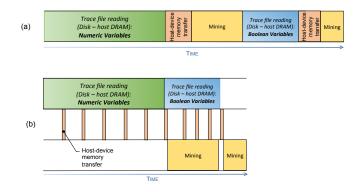

|           | 20.3.3 Data transfer and overlapping of the mining phase           |

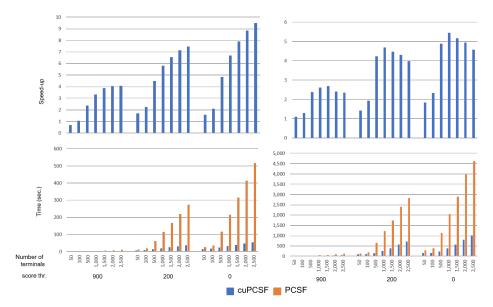

|           | 20.4 Experimental results                                          |

|           | 20.5 Concluding remarks                                            |

|           |                                                                    |

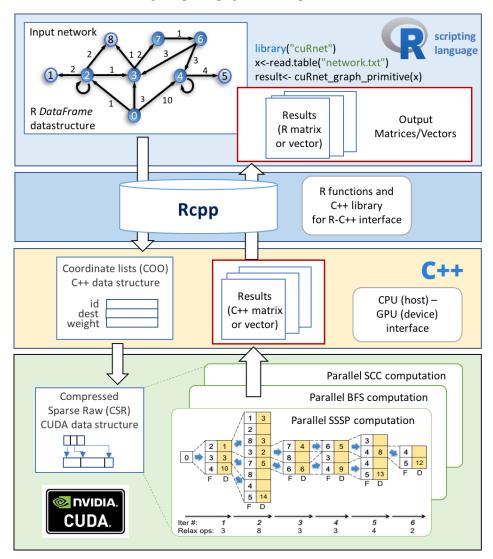

| <b>21</b> | cuRnet: an R package for graph traversing on GPU                   |

|           | 21.1 Background                                                    |

|           | 21.2 Methods                                                       |

|           | 21.2.1 Parallel implementation of Breadth-First Search for GPUs293 |

|           | 21.3 Results and discussion                                        |

|           | 21.3.1 Data                                                        |

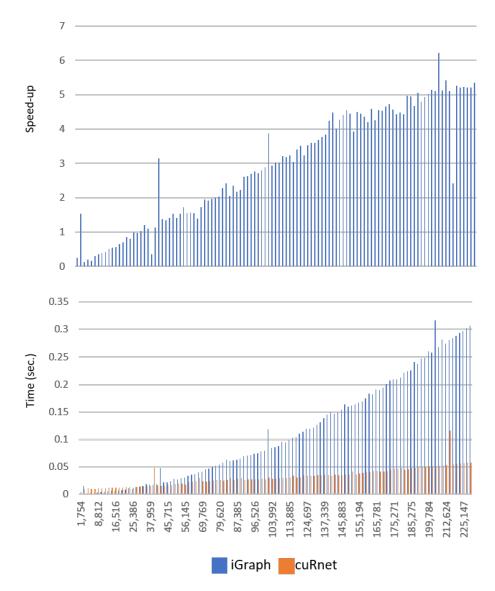

|           | 21.3.2 <i>cuRnet</i> performance                                   |

|           | 21.4 Conclusion                                                    |

| 22   | Conclusions                      | 301 |

|------|----------------------------------|-----|

| Part | VI Ph.D. Candidate's Bibliografy |     |

Contents

1

## Thesis Abstract

Graphs are a common representation in many problem domains, including engineering, finance, medicine, and scientific applications. Different problems map to very large graphs, often involving millions of vertices. Even though very efficient sequential implementations of graph algorithms exist, they become impractical when applied on such actual very large graphs. On the other hand, graphics processing units (GPUs) have become widespread architectures as they provide massive parallelism at low cost. Parallel execution on GPUs may achieve speedup up to three orders of magnitude with respect to the sequential counterparts. Nevertheless, accelerating efficient and optimized sequential algorithms and porting (i.e., parallelizing) their implementation to such many-core architectures is a very challenging task. The task is made even harder since energy and power consumption are becoming constraints in addition, or in same case as an alternative, to performance. This work aims at developing a platform that provides (I) a library of parallel, efficient, and tunable implementations of the most important graph algorithms for GPUs, and (II) an advanced profiling model to analyze both performance and power consumption of the algorithm implementations.

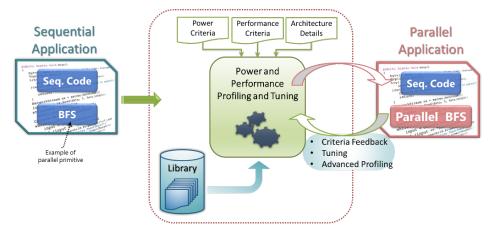

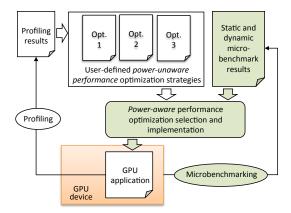

Overview of the proposed platform.

2 1 Thesis Abstract

The platform goal is twofold. Through the library, it aims at saving developing effort in the parallelization task through a primitive-based approach. Through the profiling framework, it aims at customizing such primitives by considering both the architectural details and the target efficiency metrics (i.e., performance or power).

## Performance-Oriented Implementations of Graph Algorithms for GPU

A library of the most important graph algorithms has been implemented for GPU architectures. It provides high efficient, maintainable, flexible, extendable and power-aware parallel implementations of graph algorithms. The library is focused on main graph algorithms in the literature that have huge applications in real world problems. It includes:

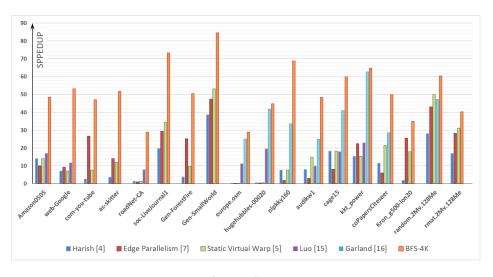

**Breadth-first search (BFS-4K).** BFS is one of the most common graph traversal algorithms and the building block for a wide range of graph applications. This work presents BFS-4K, a parallel implementation of BFS for GPUs that exploits the more advanced features of GPU-based platforms (i.e., NVIDIA Kepler) and that achieves an asymptotically optimal work complexity. An analysis of the most representative BFS implementations for GPUs at the state of the art and their comparison with BFS-4K are reported to underline the efficiency of the proposed solution.

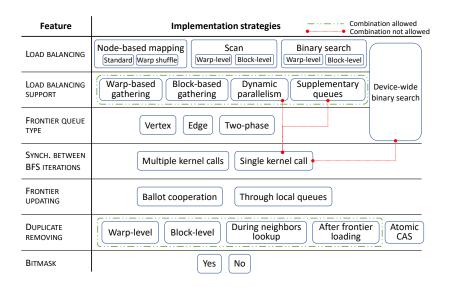

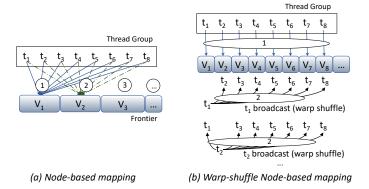

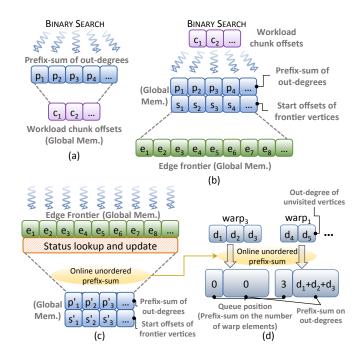

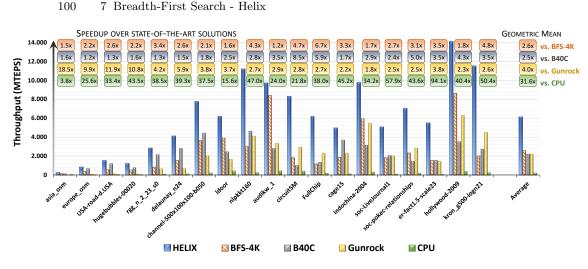

**Fully Configurable BFS (Helix).** This work presents *Helix*, a fully configurable BFS for GPUs. It relies on a flexible and expressive programming model that allows selecting, for each BFS feature (e.g., frontier handling, load balancing, duplicate removing, etc.) and among different implementation strategies of them, the best combination to address the graph characteristics. Thanks to the high reconfigurability, Helix provides high-performance and customized BFSs with speedups ranging from 1.2x to 18.5x with regard to the best parallel BFS solutions for GPUs at the state of the art.

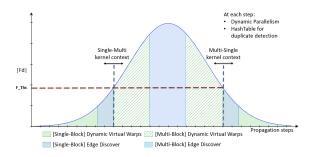

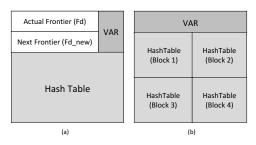

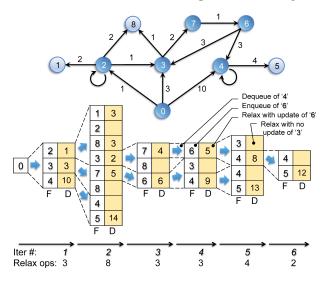

Single source shortest path (H-BF). Finding the shortest paths from a single source to all other vertices is a common problem in graph analysis. This work presents a parallel implementation of the Bellman-Ford algorithm that exploits the architectural characteristics of recent GPU architectures (i.e., NVIDIA Kepler, Maxwell, Pascal) to improve both performance and work efficiency. The work presents different optimizations to the implementation, which are oriented both to the algorithm and to the architecture. The experimental results show that the proposed implementation provides an average speedup of 5x higher than the existing most efficient parallel implementations for SSSP, that it works on graphs where those implementations cannot work or are inefficient.

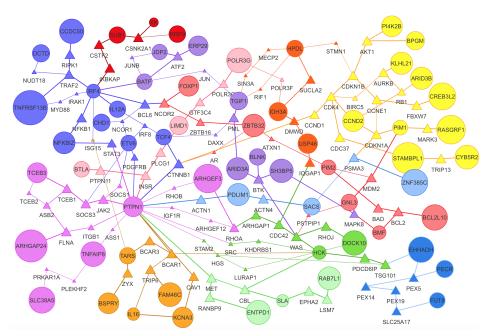

Approximate Sub-graph Isomorphism in Biological Network (AP-PAGATO). Biological network querying is a problem in bioinformatics which solution requires a considerable computational effort. Given a target and a query network, the problem is to find occurrences of the query in the network allowing nodes and edges mismatches, i.e. similarities on node labels, nodes or edges deletions. This work proposes APPAGATO, a stochastic and parallel algorithm to find

3

approximate occurrences of a query network in biological networks. APPAGATO allows nodes and edges mismatches. Thanks to its randomic and parallel nature, it results feasable on large networks compared to existing tools and also statically more accurate.

**Strongly Connected Component (SCC).** The problem of decomposing a directed graph into strongly connected components (SCCs) is a fundamental graph problem that is inherently present in many scientific and commercial applications. This work introduces a novel parametric multi-step scheme to evaluate existing GPU-accelerated algorithms for SCC decomposition in order to alleviate the burden of the choice and to help the user to identify which combination of existing techniques for SCC decomposition would fit an expected use case the most. The study confirms that there is no algorithm that would beat all other algorithms in the decomposition on all of the classes of graphs. The contribution thus represents an important step towards an ultimate solution of automatically adjusted scheme for the GPU-accelerated SCC decomposition.

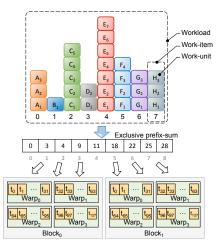

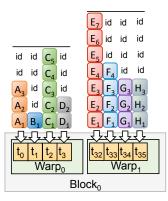

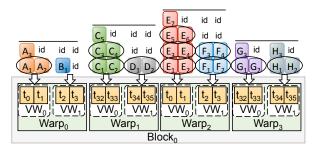

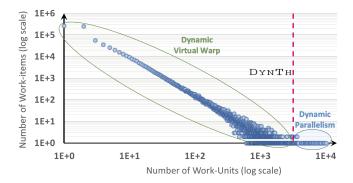

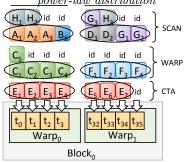

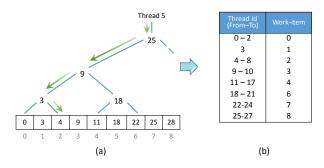

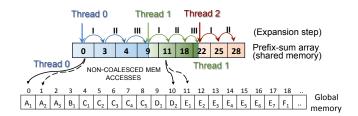

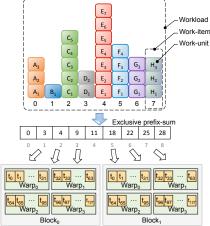

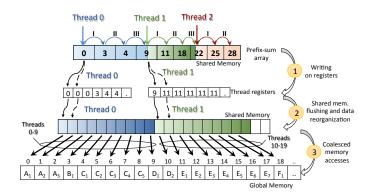

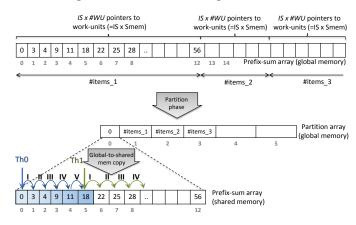

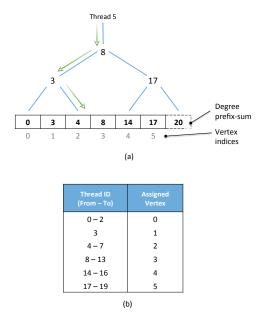

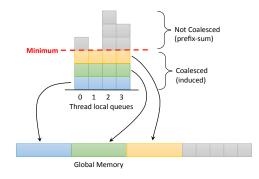

Load balancing in graph algorithms. Load balancing is a fundamental performance aspect when facing irregular problems and in particular graph algorithms. The latter strongly rely on prefix-scan values to provide an efficient memory representation. Prefix-scan is one of the most common operation and building block for a wide range of parallel applications for GPUs. It allows the GPU threads to efficiently find and access in parallel to the assigned data. Nevertheless, the workload decomposition and mapping strategies that make use of prefix-scan can have a significant impact on the overall application performance. This work presents presents Multi-Phase Search, an advanced dynamic technique that addresses the workload unbalancing problem by fully exploiting the GPU device characteristics whose complexity is sensibly reduced with respect to the other dynamic approaches in the literature.

## **Profiling and Analysis Framework**

The increasing programmability, performance, and cost/effectiveness of GPUs have led to a widespread use of such many-core architectures to accelerate generalpurpose applications. Nevertheless, tuning applications to efficiently exploit the GPU potentiality is a very challenging task, especially for inexperienced programmers. This is due to the difficulty of developing a SW application for the specific GPU architectural configuration, which includes managing the memory hierarchy and optimizing the execution of thousands of concurrent threads while maintaining the semantic correctness of the application. Even though several profiling tools exist, which provide programmers with a large number of metrics and measurements, it is often difficult to interpret such information for effectively tuning the application. This research focuses on the development of a performance model that allows accurately estimating the potential performance of the application under tuning on a given GPU device and, at the same time, it provides programmers with interpretable profiling hints.

Although, in general, the goals of algorithms and applications in computer science are to minimize measures related to time and space, another interesting and

#### 4 1 Thesis Abstract

tangible cost on a modern computing platform is the power consumption. Many analytical and quantitative models have been proposed in the literature to estimate or predict the power consumption of parallel applications but none of these approaches takes into account how algorithms and parallel programming techniques are related to power and energy consumption of the device. In particular, existing solutions provide information that is rarely useful to effectively improve the code. This work aims at developing a power consumption model and profiling framework that provides useful feedback to identify the causes of power and energy consumption of an application, to understand where and suggest how to modify the application to improve the power behavior. It includes:

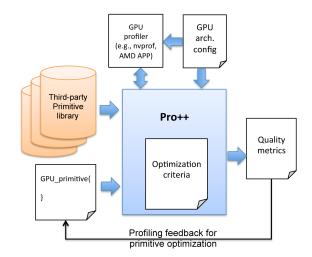

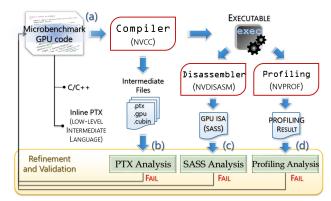

Parallel Primitives Profiling Framework (Pro++). Parallelizing software applications through the use of existing optimized primitives is a common trend that mediates the complexity of manual parallelization and the use of less efficient directive-based programming models. On the other hand, the spreading of such a primitive-based programming model and the different GPU architectures have led to a large and increasing number of third-party libraries, which often provide different implementations of the same primitive, each one optimized for a specific architecture. This work presents Pro++, a profiling framework for GPU primitives that allows measuring the implementation quality of a given primitive by considering the target architecture characteristics.

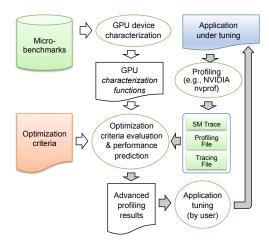

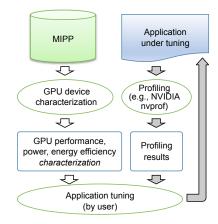

**GPU Performance Model.** Tuning applications to efficiently exploit the GPU potentiality is a very challenging task, especially for inexperienced programmers. This is due to the difficulty of developing a SW application for the specific GPU architectural configuration, which includes managing the memory hierarchy and optimizing the execution of thousands of concurrent threads while maintaining the semantic correctness of the application. This work presents a performance model that allows accurately estimating the potential performance of the application under tuning on a given GPU device and, at the same time, it provides programmers with interpretable profiling hints.

Microbenchmark Suite (MIPP). This work presents a suite of microbenchmarks, which are specialized chunks of GPU code that exercise specific device components (e.g., arithmetic instruction units, shared memory, cache, DRAM, etc.) and that provide the actual characteristics of such components in terms of throughput, power, and energy consumption. The suite aims at enriching standard profiler information and guiding the GPU application tuning on a specific GPU architecture by considering all three design constraints (i.e., power, performance, energy consumption).

**Power-aware Performance Tuning Through Microbenchmarking.** Tuning GPU applications is a very challenging task as any source-code optimization can sensibly impact performance, power, and energy consumption of the GPU device. Such an impact also depends on the GPU on which the application is run. This work presents a suite of microbenchmarks that provides the actual characteristics of specific GPU device components (e.g., arithmetic instruction units, memories, etc.) in terms of throughput, power, and energy consumption. It shows how the suite can be combined to standard profiler information to efficiently drive the application tuning by considering the three design constraints (power, per-

5

formance, energy consumption) and the characteristics of the target GPU device.

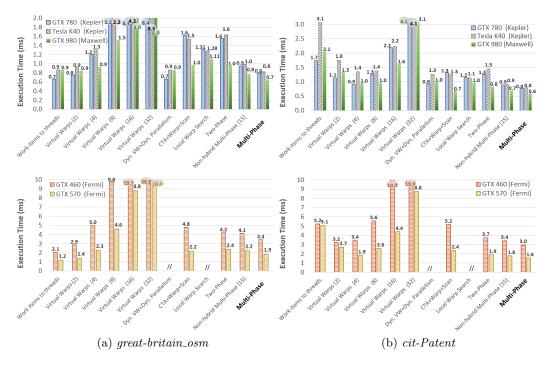

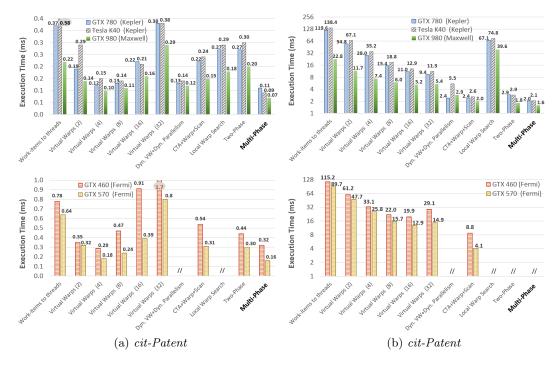

Case Study: Performance, Power, and Energy efficiency of Load Balancing Algorithms. Load balancing is a key aspect to face when implementing any parallel application for GPUs. It is particularly crucial if one considers that it strongly impacts on performance, power and energy efficiency of the whole application. This work shows and compares, in terms of performance, power, and energy efficiency, the experimental results obtained by applying all the different static, dynamic, and semi-dynamic techniques at the state of the art to different datasets and over different GPU technologies.

#### Dynamic graph representation and algorithms

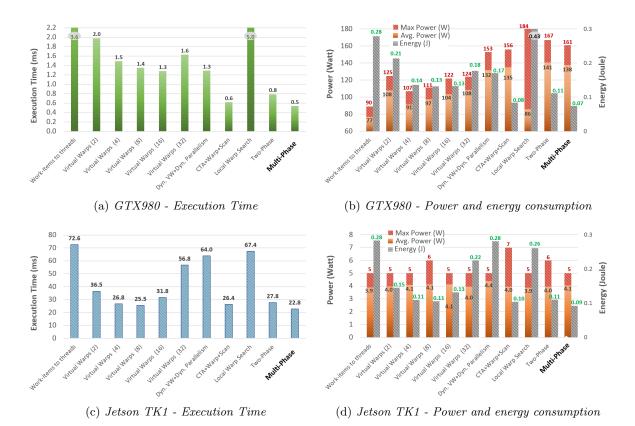

Sparse data computations are ubiquitous in science and engineering. Unlike their dense data counterparts, sparse data computations have less locality and more irregularity in their execution, making them significantly more challenging to optimize. Even more challenging is their optimization for parallel applications and algorithms. Dynamic sparse data applications are now pervasive and can be found in many domains. *Dynamic* refers to the fact that the data is changing at very high rates. For example, updates might represent the change in the current-flow of a power network or the road-congestion for a transportation network. The number of applications is considerably high and many formulations of these problems end up being either graph-based or linear-algebra based. This thesis section includes two main contributions:

Efficient Data Structure for Dynamic Sparse Graphs and Matrices (Hornet). Most of the existing formats for sparse data representations on parallel architectures are restricted to static data sets, while those for dynamic data suffer from inefficiency both in terms of performance and memory footprint. This work presents Hornet, a novel data representation that targets dynamic graph analytics and linear algebra based problems. The data structure includes an optimized memory manager that is responsible for memory allocation, reclamation, and for ensuring low overhead to represent the data during its evolution. Hornet is scalable with the input data, flexible in representing data set properties, and does not require any data re-allocation or re-initialization during the data evolution.

**K-Truss.** The KTruss of a graph is a subgraph such that each edge is tightly connected to the remaining elements in the k-truss. This work presents a novel algorithm for finding both the KTruss of the graph (for a given k), as well as the maximal KTruss using a dynamic graph formulation. The algorithm has two main benefits. The algorithm shows high work-efficiency and it is extremely scalable in contrast to past approaches.

### Applications

Invariant mining (Mangrove). Invariant mining is a promising strategy that extracts logic formulas holding between a couple (or several couples) of points

#### 6 1 Thesis Abstract

in an implementation. Such formulas express stable conditions in the behavior of the system under verification (SUV) for all its executions, which can be used to analyze several aspects in verification of SW programs and HW designs, at different abstraction levels. For complex SUV, this could require to elaborate thousands of execution traces, including millions of clock cycles, and predicating over hundreds of variables, which becomes an unmanageable time-consuming activity for existing approaches. This research activity aims at providing very efficient and flexible parallel algorithm based on advanced GPU optimization techniques and on runtime inference to avoid redundant elaboration to allow the analysis of huge SUV traces in short time.

cuRnet. R has become the de-facto reference analysis environment in Bioinformatics. Plenty of tools are available as packages that extend the R functionality, and many of them target the analysis of biological networks. Several algorithms for graphs, which are the most adopted mathematical representation of networks, are well-known examples of applications that require high-performance computing, and for which classical sequential implementations are becoming inappropriate. This work presents cuRnet, a R package that provides a parallel implementation for GPUs of the breath-first search (BFS), the single-source shortest paths (SSSP), and the strongly connected components (SCC) algorithms. The package allows offloading computing intensive applications to GPU devices for massively parallel computation and to speed up the runtime up to one order of magnitude with respect to the standard sequential computations on CPU.

Background

# Introduction

This part of the thesis presents some preliminary concepts concerning GPU (Graphic Processing Unit), CUDA programming model, and static graph representation, which facilitate the reader to better understand the context of the work.

The part is organized as follows. Section 2 summarizes the programming and architectural characteristics of the most recent GPUs that have been exploited in the following works. Besides GPU characteristics, the section focuses on the programming model of such devices (CUDA) and related advanced primitives which allows to improve the common parallel operations. Section 3 introduces the topic of static graph data structures on GPUs. It presents and compares the main important data structures and techniques applied for representing graphs on GPUs at the state of the art.

# Graphic Processing Unit (GPU)

GPU devices are massive multithreaded architectures composed by scalable arrays of parallel processors called Streaming Multiprocessors (SMs). Each SM contains a set of cores, called Stream Processors (SPs) that executes warp instructions. Each SP executes fixed-point and floating-point single-precision operations through dedicated ALU and FPU units. SPs are supported by special purpose units that execute double-precision instructions (DFU), transcendental operations (SFU), such as trigonometric functions, and load/store units to issue memory instructions and to calculate memory addresses. The number of SPs per streaming multiprocessor is fixed by the *compute capability* of the device, while the number of DFU, SFU, load/store units depends on the particular chip. On the other hand, the SM has limited instruction throughput per clock cycle. GPUs also feature a sophisticated memory hierarchy, which involves thread registers, shared memory, DRAM memory and two-level cache (L1 within a SP, while L2 accessible to all threads).

In the last NVIDIA GPU architectures, Kepler, Maxwell, Pascal and Volta, a small read-only cache per-SM (called Texture cache) is also available to reduce global memory data access.

## 2.1 Computed Unified Device Architecture (CUDA)

The threads run the same kernel concurrently, and each one is associated with a unique thread ID. A kernel is executed by a 1-, 2-, or 3-dimensional *grid* of thread *blocks*. Threads are arranged into three-dimensional thread blocks.

CUDA is a parallel computing platform and programming model proposed by NVIDIA. CUDA comes with a software environment that allows developers to use C/C++ as a high-level programming language targeting heterogeneous computing on CPUs and GPUs. Through API function calls, called *kernels*, and language extensions, CUDA allows enabling and controlling the offload of compute-intensive routines. A CUDA kernel is executed by a *grid* of *thread blocks*. A thread block is a batch of *threads* that can cooperate and synchronize each other via shared memory, atomic operations and barriers. Blocks can execute in any order while threads in different blocks cannot directly cooperate.

#### 12 2 Graphic Processing Unit (GPU)

Groups of 32 threads with consecutive indexes within a block are called *warps*. A thread warp executes in SIMD-like way the same instruction on different data concurrently. In a warp, the synchronization is implicit since the threads execute in lockstep. Different warps within a block can synchronize through fast barrier primitives. In contrast, there is no native thread synchronization among different blocks as the CUDA execution model requires independent block computation for scalability reasons. The lack of support for inter-block synchronization requires explicit synchronization with the host, which involves significant overhead.

A warp thread is called *active* if it successfully executes a particular instruction issued by the warp scheduling. A CUDA core achieves the full efficiency if all threads in a warp are active. Threads in the same warp stay idle (not active) if they follow different execution paths. In case of *branch divergence*, the core serializes the execution of the warp threads.

In modern GPU architectures (e.g., NVIDIA Kepler, Maxwell, Pascal, and Volta) each SM can handle up to 2048 threads and 64 warps concurrently. The number of warps per SM is called *theoretical occupancy* of the device. Each SM has four warp schedulers, that issue the instructions from a given warp to the corresponding SIMD core, allowing 8 instructions to be execute per clock cycle. Thread blocks are dynamically dispatched to the SMs through a hardware scheduler that works at device-level. The grid configuration and the thread block/warp scheduling strongly affects performance.